Chất nền thuỷ tinh, cách mạng mới trong ngành bán dẫn? (P2)

Phần 2 của bản dịch cho bài viết trên Semiconductor Engineering, bao gồm một số chỉnh sửa nhỏ. Đọc bài gốc tại đây https://semiengineering.com/the-race-to-glass-substrates/

Phần 1 của bản dịch: https://nguyenfamj.substack.com/p/chat-nen-thuy-tinh-trong-san-xuat-chip-p1

Với tấm nền thủy tinh, nhà sản xuất có thể đẩy giới hạn mật độ kết nối, mở đường cho mạch tích hợp chặt chẽ và phức tạp hơn. Thiết bị không chỉ nhỏ hơn, nhanh hơn mà còn tin cậy hơn nhờ đặc tính điện đồng nhất trên chất nền, đảm bảo hiệu suất ổn định qua từng lô.

Chất nền lai

Thuỷ tinh có thể kết hợp với chất nền truyền thống, tận dụng điểm mạnh về nhiệt độ ổn định và tính điện của thuỷ tinh cùng độ bền cơ học từ vật liệu như laminate hữu cơ hoặc lớp silicon trung gian. Kết quả là chất nền lai sở hữu hiệu suất tổng thể vượt trội, đáp ứng yêu cầu đa dạng của thiết kế chip hiện tại và tương lai.

Ví dụ, chất nền lai có lõi thuỷ tinh hỗ trợ truyền tín hiệu tần số cao ít tổn hao, kết hợp với lớp laminate mạ đồng để tăng độ cứng cấu trúc và hiệu quả chi phí. Cách tiếp cận này giảm đáng kể nhược điểm giòn của thuỷ tinh trong khi lại phát huy được đặc tính hiệu suất cao.

Keith Best nhấn mạnh: “Kết hợp thuỷ tinh với chất nền khác không đơn thuần là gộp ưu điểm. Đó là đạt được đặc tính hiệu suất cao chưa từng có.”

Tiêu chuẩn hóa và tương thích

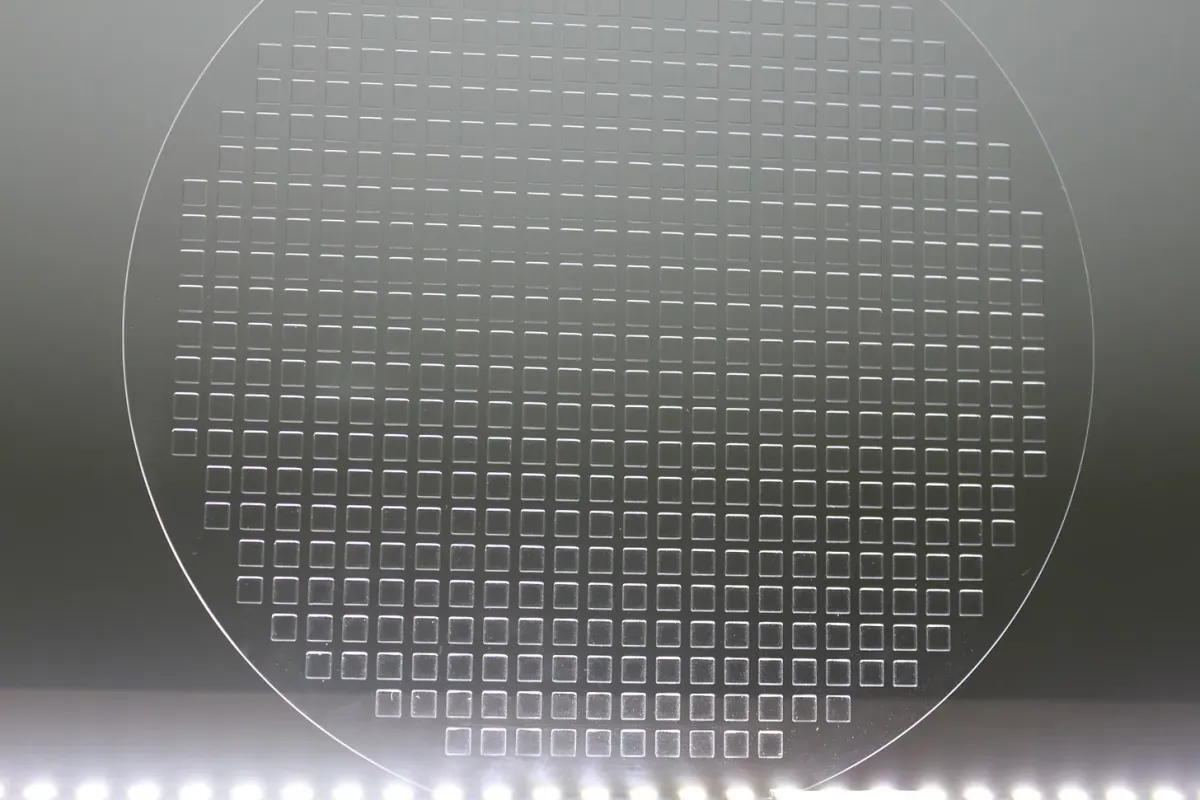

Rào cản lớn với thủy tinh là thiếu tiêu chuẩn thống nhất về kích thước, độ dày và các đặc tính. Khác với wafer silicon đã có những tiêu chuẩn toàn cầu chính xác, chất nền thủy tinh hiện chưa có quy chuẩn chung - gây khó cho nhà sản xuất thiết bị và xưởng đúc khi cần thay đổi quy trình phù hợp với những chất nền mới.

Vấn đề tương thích không chỉ giữa các loại thủy tinh mà còn giữa chất nền và thiết bị bán dẫn. Việc phối hợp đặc tính điện/ nhiệt độc đáo của thủy tinh với thiết bị là yêu cầu bắt buộc.

Chang nhận định: "Thủy tinh sẽ không được dùng cho sản phẩm hoàn thiện. Nó dành cho những ứng dụng tiên tiến nhất với những giải pháp nguồn tốt hơn. Nhưng xử lý sẽ khó khăn hơn — đó là một trong những vấn đề chính."

Khi ngành bán dẫn chuyển sang những phương pháp đóng gói tiên tiến như chiplet và 3D-IC, quy trình hậu xử lý đang biến đổi mạnh mẽ, áp dụng kỹ thuật vốn dùng trong sản xuất tiền xử lý.

Quang khắc đóng vai trò then chốt trong tạo đường khắc dưới 2µm cần thiết cho chiplet và đóng gói 2.5D/3D-IC. Tuy nhiên, kích thước siêu nhỏ này đòi hỏi vật liệu chịu được điều kiện gia công khắt khe mà vẫn duy trì tính toàn vẹn.

Travis Brist, Quản lý tiếp thị sản phẩm cấp cao tại Synopsys, cho biết: "Thách thức lớn hiện nay là tối ưu hóa công cụ quang khắc. Áp lực này ngày càng gay gắt."

Với ít hạn chế về định dạng chất nền và khả năng dùng thấu kính lớn với độ mở thấp, các nhà cung cấp đang chuyển sang đóng gói kiểu “fan-out panel-level” (FOPLP) để xử lý nhiều gói hơn trên một tấm và giảm chi phí. Ước tính FOPLP giúp giảm 30-40% chi phí so với đóng gói wafer đường kính 300mm.

Sáng tạo

Với kích thước lớn và đặc tính vật lý khác biệt, việc đạt kết nối bước nhỏ trên panel đòi hỏi kỹ thuật quang khắc tạo chi tiết siêu nhỏ mà vẫn đảm bảo độ chính xác — một điểm rất khó trên những tấm lớn dễ cong vênh.

CCL vẫn là chất nền chính cho FOPLP nhờ độ bền và hiệu quả chi phí. Thành phần sợi thủy tinh và đồng giúp CCL trở thành lựa chọn phổ biến. Tuy nhiên, cấu trúc CCL cũng khiến nó dễ biến dạng dưới ứng suất nhiệt và cơ học. Mỗi lớp có thể tạo độ lệch lớp khác nhau do biến dạng các tấm — vấn đề nghiêm trọng khi cần duy trì mẫu đường khắc đồng đều. Sai lệch nhỏ cũng có thể gây tổn thất về năng suất rất lớn.

Best giải thích: "CCL rất bền nhưng không ổn định về độ cong vênh. Hiện nhiều đơn vị đang đạt độ nhỏ đường khắc 9/12μm và nhắm tới 5/5μm. Một số muốn xuống 2/2μm — có lẽ là giới hạn của CCL. Sau đó, cuộc đua sẽ chuyển sang thủy tinh."

Tương thích không chỉ dừng ở đặc tính vật lý của thủy tinh mà còn bao gồm độ bám dính của vật liệu khác như điện môi và kim loại — vốn có hành vi khác biệt trên thủy tinh so với chất nền truyền thống.

Thiếu tiêu chuẩn ngành dẫn đến biến động hiệu suất. Khi mỗi nhà sản xuất tuân thủ thông số riêng cho thủy tinh, sản phẩm của họ có thể không tương đồng ngay cả trong cùng ứng dụng. Khi đóng gói tiên tiến hướng tới khắc nhỏ hơn và công nghệ kết nối phức tạp hơn, sự khác biệt về hệ số giãn nở nhiệt và đặc tính điện giữa thủy tinh với vật liệu khác trở nên nghiêm trọng. Thiếu tiêu chuẩn, việc tích hợp thủy tinh với công nghệ như “through-glass vias” (TGV) và microbump gặp nhiều rủi ro, ảnh hưởng năng suất và độ tin cậy.

Giải quyết thách thức này đòi hỏi hợp tác toàn ngành để xây dựng tiêu chuẩn cho thủy tinh. Các nhóm làm việc bao gồm nhà sản xuất thủy tinh, công ty bán dẫn, chuyên gia đóng gói và nhà cung cấp thiết bị phải cùng thiết lập tiêu chuẩn đáng tin cậy, nâng cao khả năng dự đoán và hiệu quả sản xuất.

Tiêu chuẩn hóa và tương thích sẽ quyết định vai trò của thủy tinh trong tương lai đóng gói tiên tiến. Chỉ thông qua thống nhất nghiêm ngặt về giao thức chung, lợi ích đầy đủ của thủy tinh mới được hiện thực hóa.

Kết luận

Với tấm nền thủy tinh, nhà sản xuất có thể đẩy giới hạn mật độ kết nối, mở đường cho mạch tích hợp chặt chẽ và phức tạp hơn. Thiết bị không chỉ nhỏ hơn, nhanh hơn mà còn tin cậy hơn nhờ đặc tính điện đồng nhất trên chất nền, đảm bảo hiệu suất ổn định qua từng lô.

Manepalli khẳng định: "Tiềm năng của thủy tinh còn rất lớn. Chúng ta thậm chí chưa khai thác lợi ích tần số cao của nó. Hãy tưởng tượng những thứ có thể tạo ra khi hoàn thiện quy trình!"